Daugelis tikrai yra girdėję apie SOI (Silicon on Insulator - silicis ant izoliatoriaus), bet ką galite pasakyti apie SON (Silicon on Nothing - silicis ant nieko)? Apie tai, tarp kitų temų, buvo kalbama didžiojoje kasmetinėje puslaidininkių konferencijoje IEDM (International Electron Device Meeting). Joje atsispindėjo tos sritys, į kurias daugiausiai investuoja puslaidininkių pramonės kompanijos.

Puslaidininkių pramonė iš visų jėgų stengiasi išvengti greitai kintančios rinkos sukeltų ekonominių sūkurių. Tai, kokią strategiją pasirinks kiekviena kompanija, labai daug priklauso nuo tos kompanijos gaminių asortimento, tačiau yra du keliai, kuriais eina visi: drastiškas gamybos kaštų mažinimas ir naujų technologijų paieškos. Kalbant aiškiau, tas, kuris sugebės pirmas patekti į perspektyvią rinką su savo inovaciniu gaminiu, padarys geriausią biznį. Visi juk žino, kad geriausiai galima pasipelnyti iš pirmųjų pavasario bulvių arba braškių.

IEDM 2001, vykusi gruodžio pradžioje Vašingtone (JAV), buvo tradicinė kasmetinė konferencija, pritraukusi pačius svarbiausius puslaidininkių rinkos dalyvius. Šįkart susidomėjimas ja buvo ypač didelis, nes ji tapo tikra technologijos naujovių vitrina.

Suabejota Moore dėsniu

Pastaruoju metu vienas svarbiausių klausimų yra, ar Moore dėsnis, anot kurio mikroschemų galimybės padvigubėja kas 18 mėnesių, galios ir ateityje. Nuomonės šioje vietoje išsiskiria: kai kurie ekspertai mano, kad jis galios dar dviem trim naujų prietaisų kartoms, o kiti tikisi lėtesnės pažangos. Trečioji grupė tvirtina, kad dėsnio fizikinės ribos dar nėra pasiektos, todėl Gordono Moore pranašystė pildysis dar labai ilgai.

Pabandysime perfiltruoti kas konferencijoje buvo pasakyta apie tai, ko galima tikėtis mikroschemų tobulinimo srityje. Tai nėra paprasta, nes 40 konferencijos sesijų buvo perskaityta daugiau kaip 200 pranešimų.

Konferencijoje paaiškėjo, kokių naujų idėjų mikroelektronikos pramonė dar turi savo arsenale. Kai kurios jų bus įgyvendintos jau kitais metais, kitų praktinio pasirodymo dar teks kiek palaukti. Bendra judėjimo kryptis yra aiški, tik kyla kitas klausimas, kaip greitai atskiroms kompanijoms pavyks ją įdiegti gamyboje.

Atmintinių fronto naujienos

Pasirodžius nešiojamiesiems elektronikos prietaisams labai išryškėjo "flash" atmintinių reikšmė. Jų pranašumas, lyginant su DRAM, yra svarbus tuo, kad išsaugo informaciją net ir tuomet, kai yra atjungiama maitinimo įtampa. Be to, atrodo, greitai išnyks vienas iš pagrindinių "flash" atmintinių trūkumų. Labai ilgai jos keliomis kartomis atsilikdavo nuo DRAM pagal atminties dydį. Dabar tai jau yra istorija.

Samsung pademonstravo pagal NAND technologiją pagamintą "flash" atmintinę, kurią sudaro 0,12 µm dydžio dariniai. Jos talpa yra 1 Gb, o plotas tėra 132 mm2. Tarp bitų magistralių ir atminties masės yra 32 viena su kita sujungtos NAND ląstelės, leidžiančios maksimaliai sumažinti lusto užimamą plotą. "Pridėtinis" paviršius, kuris dabartinėse atmintinėse, turinčiose 16 NAND ląstelių, sudaro 27 proc., sumažėjo iki 13 proc. Kiekvienos ląstelės dydis suspaustas iki 0,067 µm2. Atmintinė yra maitinama 1,8 V įtampa. Anot Samsung, visa tai jau beveik paruošta masinei gamybai.

Samsung turi naują alternatyvą ir NOR tipo "flash" atmintinėms; ir šiuo atveju panaudojo 0,12 µm technologiją. Dėl savo konstrukcijos NOR ląstelėms reikia dvigubai didesnio ploto nei NAND ląstelėms, 0,14 µm2 , bet, lyginant su konkurentų gaminamomis NOR ląstelėmis, jos yra gerokai mažesnės. Sukurtojoje atmintinėje ląstelių matrica, užtikrinanti 64 kb talpą, vis dar yra prototipo kūrimo stadijoje. NOR "flash" atmintinės yra aiškiai vertingesnės už savąsias NAND giminaites, nes jų gamyba yra paprastesnė.

Intel pranešė apie savo 32 Mb "flash" atmintinę su 0,13 µm dariniais, kurios ląstelių dydis yra 0,16 µm2. Jos yra dvigubai mažesnės už ankstesnės 0,18 µm kartos ląsteles. Atmintinė yra priderinta prie Intel 0,13 µm logikos gamybos technologinių procesų, o tai reiškia, kad jos gamybai praktiškai jau yra pasiruošta.

Pažanga matyti ir RAM kūrimo srityje. Samsung parodė 1,29 µm2 ploto SRAM ląstelę, pagamintą CMOS technologijos būdu bei 120 nm dydžio darinius. Bandymui buvo padaryta 8 Mb atmintinė. Budėjimo režime ji vartojo mažesnę kaip 10 µA srovę, o maitinimo įtampa buvo 2,2 V.

Nors šiandieninė krizė kamuoja DRAM rinką, šio tipo atmintinės ir toliau vis tobulinamos. Samsung parodė, ką galima pasiekti pasitelkus mažesnius nei 100 nm darinius. Įrašymo ir nuskaitymo spartos kaip sugebėjimas išsaugoti įrašytuosius duomenis artėja prie ribinių verčių, kadangi vis daugiau reikšmės pradeda įgauti parazitinės įvairių komponentų sąveikos. Iki šiol yra daug neišspręstų medžiagotyros klausimų. Ypač tai taikytina atminties ląstelių kondensatoriams.

Feromagnetinės RAM turi problemų

Tokijo technologijos institutas padarė pranešimą apie FeRAM tyrimų būklę ir paryškino čia pasirodžiusias problemas. Iki šiol susiduriama su nemažai sunkumų didinant jų integravimo laipsnį. Tai atspindi ne vienas gamintojas taip ir nesugebėjęs pasiūlyti megabitinių FeRAM atmintinių. Bet pati svarbiausia problema, atrodo, yra grynai technologinė: šiandien žinomų feromagnetinių sluoksnių kristalizavimosi temperatūra yra gerokai aukštesnė nei gali atlaikyti po tais sluoksniais esantys CMOS grandynai. Todėl tuos sluoksnius reiktų dar suploninti, bet tai yra lengviau pasakyti nei padaryti. Pirmieji bandymai su 13 nm storio sluoksniais parodė, jog šiuo atveju su puslaidininkiais neturėsime jokių problemų, jeigu sluoksnių kristalizavimosi temperatūrą sugebėsime numušti žemiau 200 oC.

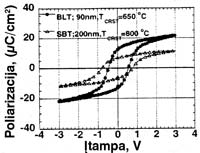

1 pav. Senesnės feroelektrinės medžiagos SBT ir naujojo feroelektriko BLT histerezės kreivės. BiLaTi leidžia naudoti plonesnius sluoksnius, mažesnes kristalizavimo temperatūras ir trumpesnes kreipties trukmes.

Hynix Semiconductors pademonstravo bandomąją 1 Mb FeRAM, pagamintą naudojant 0,35 µm CMOS technologiją. Lusto dydis siekė 50 mm2. Buvo minimos 170 ns dydžio kreipties į atmintinę trukmės (esant 5 V maitinimo įtampai). Gamintojo duomenimis, šios nelakiosios atmintinės duomenų saugojimo trukmė yra apie 10 metų. Ištrynimo ir pakartotinio įrašymo ciklų skaičius - 1010. Atmintinėje informacija saugoma ne SBT (SrBiTa), o plonuosiuose BLT (BiLaTi) sluoksniuose (žr. 1 pav.).

Dėmesį patraukė bendras Intel ir Ovonyx mokslinis projektas: nelakioji atmintis, vartojanti chalkogenidus. Pradžioje pažiūrėkime, kaip ji veikia. Pačiai idėjai, tiesą sakant, jau yra apie trisdešimt metų, o ją, kartu su D. L. Nelsonu ir R. G. Neale, pasiūlė legendinis Intel įkūrėjas Gordonas Moore. Chalkogenais yra vadinami šeštosios Mendelejevo periodinės sistemos grupės elementai, pavyzdžiui, siera, selenas ir telūras. Atmintis remiasi terpės fizikinės fazės virsmu. Informacija įrašoma registruojant virsmą iš amorfinės į polikristalinę fazę, ir atvirkščiai. Tas virsmas chalkogenuose aktyvuojamas terminiu būdu - 10 ns trukmės elektriniu impulsu. Toks impulsas perveda atmintį į amorfinę būseną, todėl yra naudojamas kaip "Reset" veiksmas. Norint atminties terpę pervesti į būseną "Set", yra reikalingas 100 ns trukmės impulsas. Jau buvo be jokio degradavimo išbandyta 1012 tokių ciklų.

Analoginiai ir skaitmeniniai signalai

Visi konstruktoriai svajoja sutelkti visus aktyviuosius ir pasyviuosius komponentus viename CMOS skaitmeniniame grandyne, kuris, priedo, leistų realizuoti mūsų norimas analogines funkcijas. Iki šios vizijos įgyvendinimo mes vis dar esame labai toli, nežiūrint to, kad jau esama gana sudėtingų mišrių signalų grandynų. Vienintelis šios problemos sprendimo būdas yra gamybos kaštų sumažinimas. Kiekvienas papildomas fotolitografijos šablonas tiktai padidina gamybos savikainą.

Texas Instruments pranešė apie savo darbus integruojant analogines ląsteles ir mažai energijos suvartojančią CMOS skaitmeninę technologiją. Iš realizuotų pasyviųjų komponentų reikia paminėti polikristalinio silicio varžas su mažu temperatūriniu koeficientu bei n-poly kondensatorius, kuriuos galima panaudoti, kai talpą reikia paderinti iki 30 proc. Visiems šiems komponentams pakanka vieno fotošablono. Skaitmeniniai grandyno elementai maitinami 1,5 V įtampa, o analoginiai - maitinimo įtampą keičiant nuo 1,5 iki 3,3 V.

2 pav. Triukšmo lygio priklausomybė nuo dažnio, išmatuota Philips pagamintame 0,18 µm CMOS technologijos grandyne. Triukšmo lygis yra mažesnis nei 1 dB tol, kol dažnis neviršija 8 GHz.

Philips ir jo partneriai atkreipė dėmesį, kad iki šiol skaitmeninių CMOS procesų mažinimui naudoti scenarijai nelabai tinka realizuojant grandynuose analogines funkcijas. Komponentų degradavimui spartėjant triukšmas išauga. Čia dar reikia pridurti, kad norint sumažinti kiekvieną matmenų žingsnį, reikia keisti gamybos procesus, nes kitaip nepavyks realizuoti visų analoginės dalies funkcijų.

Mitsubishi Electric papasakojo apie kompanijos vykdomus tyrimus, parodžiusius, jog galima integruoti analoginius aukštadažnius komponentus ir logiką net ir tada, kai maksimalus dažnis esti 135 GHz (!). Kai buvo remtasi bazine SOI-CMOS 0,18 µm technologija, mažiausias užtūros ilgis buvo 70 nm. Kai dažnis buvo 40 GHz, buvo vis dar stebėtas 11 dB stiprinimas.

Philips taip pat judėjo ta pačia kryptimi: jie panaudojo 0,18 µm darinius ir pasiekė didžiausią osciliatoriaus dažnį, lygų 150 GHz, ir perėjimo dažnį - 70 GHz. Pritaikymų, kuriems yra svarbus apie 10 GHz dažnis, yra įdomus mažas triukšmo lygis: kai dažnis yra 8 GHz, jis vis dar nesiekia 1 dB (2 pav.).

Pakeliui į 100 nm darinius

Trys kompanijos - IBM, Infineon ir United Microelectronics - pranešė sukūrusios CMOS elementą su mažiausiomis 50 nm dydžio detalėmis; toks elementas tinka mikroprocesoriams ir "įterptosioms" procesorių šerdims. Šitaip buvo žengtas pirmasis žingsnis link 100 nm technologijos ateities, planuojamos su devyniais metalizacijos sluoksniais bei dielektrikais su mažomis skverbtimis. Žiediniuose osciliatoriuose minėtieji elementai pademonstravo 7,7 ps lėkio trukmę esant 1 V įtampai ir 6,6 ps esant įtampai 1,2 V. Šitokia technologija yra daug žadanti, bet vienas kitam prieštarauja du reikalavimai: aukšta kokybė ir mažos budėjimo režimo srovės.

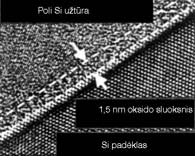

3 pav. Pagerinto Intel 130 nm CMOS lusto ribinės srities po užtūra vaizdas. Matyti labai plonas (1,5 nm) užtūros dielektriko sluoksnis, skiriantis polikristalinio silicio užtūrą nuo silicio padėklo.

AMD ir Motorola kartu sukūrė 100 nm technologiją, kuria remiantis jau pavyko pagaminti eilę svarbių komponentų, pavyzdžiui, logiką, nelakiąją atmintį ir analoginį bloką. Užtūros ilgiai kito nuo 65 iki 90 nm priklausomai nuo pritaikymo (trumpesnės užtūros mažesnės galios komponentams). Šios grandynų šerdys maitinamos ir 2,5, ir 3,3 V įtampa. Galima panaudoti iki devynių vario metalizacijos takelių. Technologija taikoma ir silicio, ir SOI gaminiams.

Intel pateikė patobulintą 130 nm technologiją, kuria galima pagaminti optimizuotus tranzistorius su 60 nm ilgio užtūromis. Dėl to tranzistorių parametrai ženkliai pagerėjo. Nors naudojama tradicinė 248 nm litografija (konkurentai jau yra įdiegę modernesnę 193 nm litografijos technologiją), ji yra išnaudota iki pat galo. Patobulinti komponentai maitinami 0,7-1,4 V įtampa, todėl galima kalbėti apie nedidelę sunaudojamą energiją. 16 Mb SRAM, kuris buvo pagamintas kaip bandomoji struktūra, dirbo 2 GHz takto dažniu (esant 1,4 V įtampai).

Silicis ant nieko

SON, silicis ant nieko, ne, tai nėra rašybos klaida. Turėsite su tuo apsiprasti. Apie ką yra kalbama? Stengiantis pagerinti lusto kokybę dažnai yra atsiremiama į medžiagos sąlygotą parazitinę talpą, ribojančią maksimalų dažnį. Šios parazitinės talpos sprendimo kelias jau seniai yra aiškus: didesnį dažnį būtų galima pasiekti, jei silicis būtų patalpintas ant gerai izoliuoto pagrindo. Favoritu šioje srityje iki šiol buvo SOI (Silicon on Insulator) technologija. Dėl to, kad iki šiol nebuvo didesnių tos technologijos pasiekimų, kalti ne jos parametrai, o papildomai didėjanti kaina. Tiesą sakant, ši technologija yra gana brangi, todėl tinkama tik brangiems lustams. Bet mobilieji telefonai turi būti pigūs, todėl brangūs lustai jiems netinka.

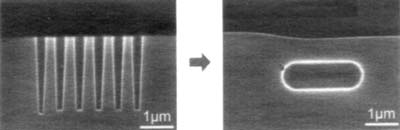

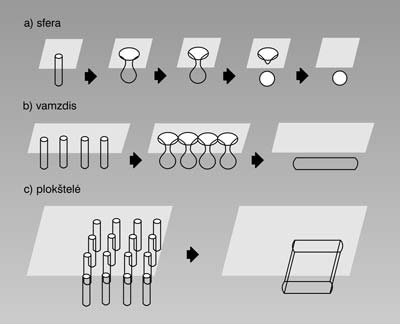

Prieš dvejus metus IEDM konferencijoje Toshiba parodė, kaip silicyje galima sukurti oro skyles (žr. 4 pav.). Oras yra puikus izoliatorius, todėl buvo stengtasi ant "oro pagalvių", o ne ant kieto dielektrinio pagrindo, patalpinti ir silicio tranzistorius. Technologija vadinama silicis ant nieko, o angliškai Silicon on Nothing (SON).

4 pav. Šitaip Toshiba gamina tuštumas silicio padėkluose. Pradžioje išėsdinamos šešios gilios skylės. Pakaitinus iki 1100 oC, jos susilieja į vieną ertmę su bendru stogeliu.

Buvo išklausyti du šiai temai skirti pranešimai. STMicroeletronics pranešė apie pirmąjį 80 nm MOSFET tranzistorių, kuriame 20 nm storio silicio kanalas buvo virš tokio pat storio "dėžutės". Skaičiavimais įrodyta, kad tranzistoriaus parametrai, lyginant juos su tradicine technologija gamintais prietaisais, pagerėjo 30 proc.

Toshiba toliau vystė savo idėją ir savo pristatytame SON-MOSFET tranzistoriuje panaudojo tikrai mažas tuštumas (ESS - Empty Space in Silicon). Vienoje pusėje tuštuma buvo 3,5 µm pločio ir 0,3 µm storio, o kitame gale jos skersmuo tebuvo tik 80 nm (žr. 5 pav.). Iki šiol tik dalinai pavyko pasiekti trokštamą parazitinės talpos sumažėjimą, nes parametrai pagerėjo tik 8 proc.

5 pav. Taip silicyje galima gauti dideles ertmes. Visada pradedama nuo vieno šulinėlio. Norint gauti didesnes tuštumas, reikia išėsdinti tokių šulinių matricas.

Vienlustė sistema

Viena pagrindinių šiųmetinių IEDM temų buvo kelių į vis mažesnius darinius paieška. Čia reikėjo suderinti mažiausiai du skirtingus reikalavimus. Pirma, atskirų komponentų sunaudojama energija turėjo būti kuo mažesnė, kadangi didesnio integravimo laipsnio dėka luste telpa daugiau tranzistorių, o tai reiškia, kad daugiau išskiriama šilumos. To galima pasiekti mažinant maitinimo įtampą, bet čia tenka susidurti su atskirų komponentų parametrų pablogėjimu.

Antra, buvo norima sumažinti ir viso lusto paviršiaus plotą. Kol kas daugiausia kalbama apie SRAM atmintines, kurias norėta įterpti į logikos grandynus. SRAM atminties ląstelė dėl grynai techninių priežasčių užima ženkliai didesnį paviršiaus plotą nei DRAM ląstelė. Todėl siekta pirmiausia į logiką integruoti eDRAM (e čia žymi "embedded" - įterptoji). Jos yra nuo penkių iki aštuonių kartų mažesnės už savąsias giminaites SRAM, nors ir ne tokios galingos, kai palyginame parametrus.

Ir NEC, ir IBM/Infineon/UMC pristatė 0,13 µm eDRAM technologijas. Abiem atvejais atmintinės veikė nuo 1,2 V ir buvo suderintos su logika, bet turėjo ir kai kurių skirtingų bruožų. NEC sukūrė 16 Mb bandomąjį lustą, turintį 3 ns dydžio kreipties trukmę. Papildomai patobulinus tikimasi tą trukmę sumažinti iki 2,2 ns. Iki tokių trumpų kreipties trukmių kitoms trims kompanijoms dar teks paplušėti: kol kas konsorciumas esant 1,5 V maitinimo įtampai tepasiekė 6 ns ir 8 ns esant 1,2 V maitinimo įtampai. Išbandytos 16 ir 32 Mb bandomosios matricos, kuriose pirmąkart eDRAM lustuose buvo panaudota vario metalizacija ir mažos dielektrinės skverbties dielektrikas. Bet IBM/Infineon/UMC pavyko optimizuoti savo prietaisą mažai budėjimo režime tekančiai srovei. Kol kas jis yra maitinamas 1,5 V įtampa.

Toshiba ir Sony žengė vienu žingsniu toliau ir pranešė apie 100 nm CMOS technologiją, leidžiančią viename luste integruoti ir eDRAM, ir analoginius komponentus. Technologija skiriama mažai energijos suvartojantiems portatyviems įrenginiams. Todėl maitinimo įtampa yra vos 1,2 V.

Pavojingos jungtys

Atskira pranešimų sesija buvo skirta problemai, kuri iškilo tik pastaruoju metu: lustų jungčių ateities technologijoms. Dėl besitęsiančio "giga-integravimo" luste esančių metalo takelių ilgis nuolat didėjo. Tai turėjo ženklių, negatyvių poveikių prietaiso funkcijoms, ypač aukštadažnėms savybėms, nuostoliams bei signalo vientisumui (dėl lėkio trukmės sąlygotų efektų). Paminėsime tik vieną pavyzdį: 1 mm ilgio jungties takeliuose atsiradusi RC delsa šešis kartus viršijo tranzistoriaus vidaus lėkio trukmę. Taigi, nebepakanka tik sukurti spartesnį tranzistorių; dabar veikos spartą jau ima diktuoti laidininkai.

Džordžijos technologijos institute ši problema nagrinėjama jau porą metų. Dilemos sprendimo kelią specialistai mato koncepcijoje "Reverse Scalling", kuri numato gaminti RC darinius pačiame puslaidininkyje (o ne pradžioje sukurti grandyno schemą ir po to sujunginėti ją lusto paviršiuje). Todėl reikia žiūrėti į mažus laidininko takelius kaip į bangolaidžius, turinčius savo varžą (pavyzdžiui, 50 Omų). Ateities mobiliųjų telefonų aukštadažniams komponentams tokia koncepcija bus privalomas dalykas. Grynai fiziškai labai svarbus vaidmuo tenka talpuminių nuostolių mažinimui. Labai svarbūs čia yra ir didelę dielektrinę skverbtį (nuo 2,0 iki 2,2) turintys izoliatoriai.

Kita galimybė slypi naujoje ir dar nevisiškai apibrėžtoje jungčių architektūroje, kuri leidžia simetriškai ir sinchroniškai paskirstyti luste takto dažnį. Kelią sutrumpinti įmanoma pasitelkus trečią dimensiją. Tokių lustų prototipai jau yra - tai mikrofotonikos, naudojančios polikristalinio silicio bangolaidžius ir kristalinius filtrus, taikymo sritis.

Vidiniai WLAN

UCLA (Kalifornijos universitetas Los Angeles) jau kuria naujos lustų kartos pamatus. Kokia jungčių sistema bus naudojama tada, kai lustui teks susidoroti su labai didelės spartos, pavyzdžiui, 100 Gb/s, duomenų srautais viename kanale, ar kada jam reiks sutankinti kanalus į bendrą 20 Tb/s srautą? Šiandien tokius srautus dar sunku ir įsivaizduoti. UCLA mokslininkai siūlo tokiu atveju naudoti miniatiūrinius bevielius LAN tinklus. Prieš lustą įrengiama bevielė aukštadažnė paskirstymo sistema, naudojanti talpuminius ryšius artimojo lauko antenų vietoje. Kitos antenos bus išoriniuose lusto metalizacijos paviršiuose. Kryžminės signalų sąveikos galima išvengti parinkus tinkamą moduliavimo būdą. Los Angeles jau yra dirbama su 4 GHz takto dažniu ir 10 GHz nešlio dažniu.